# **Rig Documentation**

Release 2.4.1

**Project Rig**

May 13, 2018

# Contents

| 1  | Getti  | ing started                                        | 3   |

|----|--------|----------------------------------------------------|-----|

|    | 1.1    | Installation                                       | 3   |

|    | 1.2    | Tutorial: From 'hello world' to a full application | 4   |

|    | 1.3    | Tutorial: Controlling SpiNNaker machines           |     |

|    | 1.4    | Tutorial: Selecting routing keys with BitField     | 40  |

|    | 1.5    | Quick-start examples in under 10 lines of code     | 47  |

| 2  | Refe   | rence manual                                       | 53  |

|    | 2.1    | Data packaging for SpiNNaker                       | 53  |

|    | 2.2    | Graph-to-machine mapping                           | 61  |

|    | 2.3    | Execution control and machine management           | 96  |

|    | 2.4    | Standalone utility applications                    | 137 |

| 3  | Indic  | ies and Tables                                     | 143 |

| Py | thon N | Module Index                                       | 145 |

Rig is a Python library which contains a collection of complementary tools for developing applications for the massively-parallel SpiNNaker architecture. First and foremost, Rig aims to present a light-weight, well tested and well documented interface for SpiNNaker application developers.

# CHAPTER 1

# Getting started

If you're new to Rig, here are two options for getting started: If you're feeling impatient and want to start playing, take a look at *some of the ten-line quick-start example programs*. Alternatively the *'hello world' to circuit simulator tutorial* gives a detailed introduction to building real-world SpiNNaker applications using Rig (still in under 400 lines of heavily commented Python).

# **1.1 Installation**

**Note:** Since Rig is a library rather than a standalone tool, most end-users will find that it is automatically installed as a dependency of some other application which they have installed, rendering these steps uncessary.

# 1.1.1 From PyPI via pip (Recommended)

The latest stable release can be installed from the Python Package Index using:

\$ pip install rig

Note that if you do not already have Numpy installed, this will be downloaded by the above command and may take some time to install.

#### 1.1.2 From source

You can install Rig from downloaded source code using setuptools as usual:

```

$ git clone https://github.com/project-rig/rig.git rig

$ cd rig

$ python setup.py install

```

If you intend to work on Rig itself, take a look at the DEVELOP.md file in the repository for instructions on setting up a suitable development environment and running tests etc.

# 1.1.3 Optional Extras

The following extra packages may also be installed in addition to Rig to enable additional functionality.

#### rig\_c\_sa (for faster placement)

```

$ pip install rig_c_sa

```

The rig\_c\_sa library is used by the CKernel for the *simulated annealing placement algorithm*. This kernel, written in C, can be 50-150x faster than the PythonKernel supplied in the basic Rig installation.

# 1.2 Tutorial: From 'hello world' to a full application

In this tutorial we'll walk through the process of building a SpiNNaker application using the Rig library. This series of tutorials builds up from 'hello world' to eventually building full-blown digital circuit simulator. This tutorial is aimed at people who wish to build applications for SpiNNaker and gives a broad overview of how a SpiNNaker application might be structured and how Rig can be used to handle the boring details of interacting with and using a SpiNNaker machine.

**Note:** This tutorial presumes you are moderately familliar with Python and C and have some basic familiarity with the 'Spin1 API' and SARK libraries used to write software which runs on SpiNNaker itself.

### 1.2.1 00: Introduction

In this tutorial we'll walk through the process of building a SpiNNaker application using the Rig library. This series of tutorials builds up from 'hello world' to eventually building full-blown digital circuit simulator.

In *part 01* we build a simple hello world application demonstrating how Rig can be used to load and run programs on SpiNNaker.

In parts 02 and 03 we get the hang of reading and writing data into SpiNNaker.

In *part 04* we use what we have learned to build a proof-of-concept circuit simulator. This implementation can only simulate one circuit and uses hand-written routing tables and manually assigns work to SpiNNaker's processors.

In *part 05* we rewrite our circuit simulator as if it were a real application. We design a simple API for describing circuits and use Rig's automatic place and route facilities to automatically map our circuit simulations onto the SpiNNaker machine.

The digital circuit simulator we'll be building in this tutorial closely follows the program structure used in realworld SpiNNaker applications. Though only a very small program (under 400 lines of heavily annotated Python) our simulator goes through almost all of the steps real neural simulation applications do, including implementing a high-level domain-specific 'language' for describing simulations. With luck, after completing these tutorials you will have an understanding of how to go about building your own SpiNNaker applications.

Before getting stuck in, we'll take a look at how a typical SpiNNaker application is structured and highlight how Rig fits into this picture.

#### SpiNNaker applications and Rig

Though SpiNNaker is usually described as a 'computer', in practice most applications would be more accurately described as using SpiNNaker as a co-processor or an accelerator. As a result, most applications are written in two parts:

- **SpiNNaker application kernels** A collection of small C (or C++) programs which run on SpiNNaker's application cores. These programs do the 'real' work in most applications, for example simulating neural behaviour, recording results, or playing back artificial stimuli.

- **Host application** A program which runs on a host computer connected to your SpiNNaker machine, commonly written in Python. This program handles the conversion of high-level user input into raw data the SpiNNaker application kernels can process, loads software and data onto the SpiNNaker machine and retrieves and processes results.

Though the SpiNNaker application kernel is responsible for most of the actual computation, the host program is often more complex. Rig is a library which helps with the process of writing host applications by providing tools and functions which simplify the task of interacting with and programming a SpiNNaker machine.

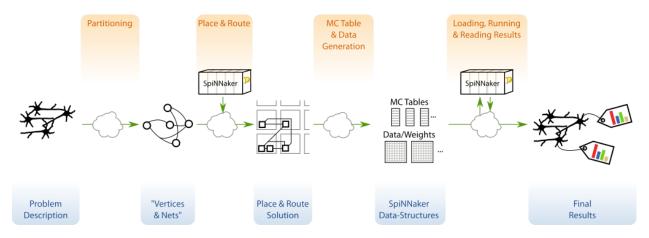

In this tutorial we'll be building an application which follows the program structure used by the host programs of many existing neural simulation tools (e.g. Nengo SpiNNaker and PyNN SpiNNaker). This program structure is illustrated in the figure below:

Most SpiNNaker applications provide a domain-specific API for describing whatever is to be simulated. This description is then *partitioned* into a graph of SpiNNaker-core-sized (*vertices*) which communicate with each other (via *nets*). This first step is usually very application specific and so Rig does not provide any functions to help.

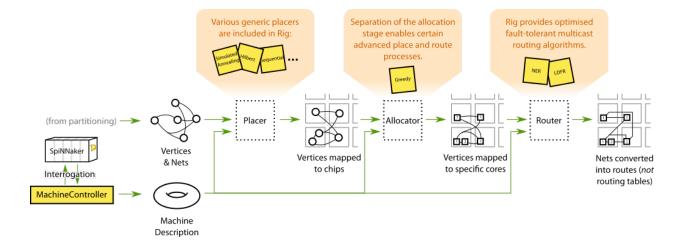

In the place and route phase of application execution, the graph of vertices and nets is mapped onto specific cores and routes in SpiNNaker's network. Rig provides a number of utilities and algorithms for performing place and route tasks for SpiNNaker applications in the *rig.place\_and\_route* module. The figure below illustrates how Rig breaks place and route into three stages: placement, allocation and routing. In most applications this process can be handled automatically by a simple wrapper function but more advanced applications can customise the process.

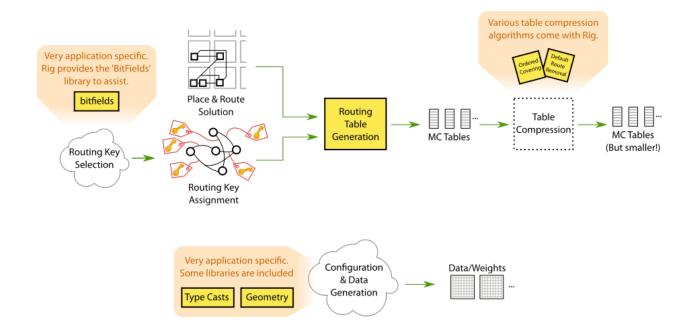

In the next phase of execution a typical application generates configuration data and routing tables which will be used by SpiNNaker application kernels (illustrated below). Though generating configuration data is highly application specific, Rig provides a limited set of libraries such as *rig.type\_casts* for converting between floating and fixed point numbers, and *rig.geometry* for dealing with machine geometry. Rig also provides libraries to assist in selecting routing keys (*rig.bitfield*) and generating and compressing SpiNNaker routing tables (*rig.routing\_table*).

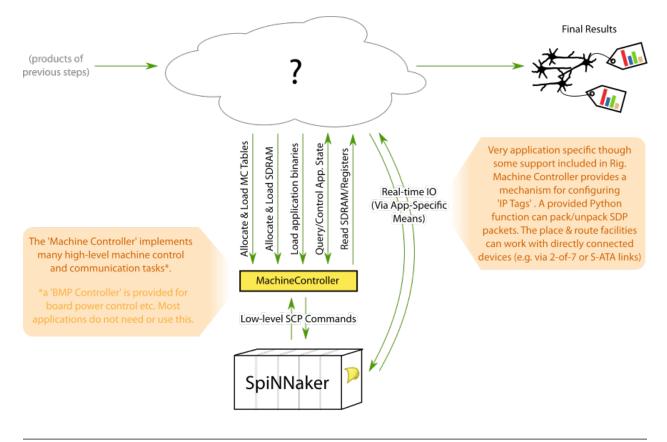

In the final stage of execution (illustrated below), the SpiNNaker application kernels are loaded onto the SpiNNaker machine along with the generated configuration data and routing tables. Results are retrieved when computation completes. Rig provides a *MachineController* class which provides an efficient and high-level interface for

controlling and interacting with a SpiNNaker machine. Development of custom, real-time interaction with running SpiNNaker application kernels is also supported but remains a largely application specific task.

**Note:** It is important to note that the Rig library does not assume or rely on this particular program structure. Rig can be (and is) used in numerous applications with widly different structures. Examples include interactive use in the Python interpreter, cabling validation software and site-wide SpiNNaker job management and machine sharing.

#### You will need...

Before you start this tutorial assumes you have the following set-up and working:

- 1. An ARM cross-compiler. In this tutorial we presume GCC which can be downloaded and installed from Launchpad or from the package managers of good Linux distributions.

- The latest version of the 'spinnaker\_tools' low-level software package which can be downloaded from the SpiN-Naker web pages.

- A SpiNNaker machine. Any size from a 4-chip SpiNN-2 or SpiNN-3 board upwards will do. To make sure everything is working correctly, make sure you can get the example 'hello' app supplied with 'spinnaker\_tools' to compile and run (see the 'spinnaker\_tools' README).

- 4. A working Python 2 or Python 3 environment with Rig *installed*.

Without further delay, proceed to part 01.

### 1.2.2 01: Hello World

In this classic example we make a SpiNNaker application which simply prints "Hello, world!" on one core and then exits.

The source files used in this tutorial can be downloaded below:

- Host program

- hello.py

- SpiNNaker kernel

- hello.c

- Makefile

As is traditional, our first application will simply print 'Hello, world!' and exit. In this example our SpiNNaker application kernel will simply write its greeting into memory on a SpiNNaker chip and then terminate. Our host program will:

- Load the application kernel

- Instruct SpiNNaker to run it

- Wait for the kernel to terminate

- · Retrieve the message from SpiNNaker's memory and print it

- Clean up and quit

#### **SpiNNaker Application Kernel**

We start by writing the SpiNNaker application kernel itself which consists of a single call to io\_printf in hello. c.

```

#include "sark.h"

void c_main(void)

{

io_printf(IO_BUF, "Hello, world!\n");

}

```

This call writes our famous message to the "IO buffer", an area of system memory in each SpiNNaker chip which we can later read back from the host.

To compile our application we can use the standard two-line makefile:

```

APP := hello

include $ (SPINN_DIRS) / make/app.make

```

To produce a compiled hello.aplx file ready for loading onto SpiNNaker, simply type:

\$ make

**Note:** This makefile presumes your shell environment is set up correctly to use the 'spinnaker\_tools'. This can be done by running:

```

$ source /path/to/spinnaker_tools/setup

```

#### Host-side application

Now that we have our compiled binary we must boot our SpiNNaker machine, load the application onto a core and then read back the IO buffer. We *could* do this using the *ybug* tool included with 'spinnaker\_tools' but since we're building toward a real application we'll write a Python program which will automate all these steps.

**Note:** Even though we'll be writing our host programs in Python without using 'ybug', the 'ybug' tool remains a very useful debugging aid during development can can be safely used alongside your host application.

In our host program we'll use a part of the 'Rig' library called *MachineController* which provides a high-level interface for communicating with and controlling SpiNNaker machines. The first step in our program is to create an instance of the *MachineController* class to communicate with our SpiNNaker board:

```

import sys

from rig.machine_control import MachineController

mc = MachineController(sys.argv[1])

```

Note that we take the hostname/IP of the board as a command-line argument to avoid hard-coding it into our script.

To boot the machine we use the boot () method. If the machine is already booted, this command does nothing.

mc.boot()

Next we'll load our application using the  $load_application()$  method. This method loads our application onto core 1 of chip (0, 0), checks it was loaded successfully and then starts the program executing.

mc.load\_application("hello.aplx", {(0, 0): {1}})

**Note:** *load\_application()* can load an application onto many cores on many chips at once, hence the slightly unusual syntax.

When a SpiNNaker application kernel's c\_main function returns, the application goes into the exit state. By using wait\_for\_cores\_to\_reach\_state() we can wait for our hello world application to finish executing.

mc.wait\_for\_cores\_to\_reach\_state("exit", 1)

After our application has exited we can fetch and print out the contents of the IO buffer to see the message printed by the application kernel. The buffer can be read using  $get_iobuf()$ . By convention Rig uses the name p – for processor – when identifying cores.

print(mc.get\_iobuf(x=0, y=0, p=1))

As a final step we must send the "stop" signal to SpiNNaker using *send\_signal()*. This frees up any resources allocated during the running of our application.

```

mc.send_signal("stop")

```

#### **Running our application**

Our script is now finished and can then be executed like so:

```

$ python hello.py BOARD_IP_HERE

Hello, world!

```

**Note:** The *boot ()* command can take a few seconds to complete if the machine is not already booted. If the machine is already booted, the script should run almost instantaneously.

Once the excitement of being greeted by a super computer has worn off, it's time to set SpiNNaker to work on some 'real' computation. Let's head onward to *part 02*.

# 1.2.3 02: Reading and Writing SDRAM

Most interesting SpiNNaker application kernels require some sort of configuration data, and produce result data, which must be loaded and read back from the machine before and after executing respectively. As a result, a typical host program will:

- Allocate some memory on any SpiNNaker chips where an application kernel is to be loaded

- Write configuration data into this memory

- Load and run the application kernel

- Read and process the result data written into memory by the kernel

To illustrate this process we'll make a SpiNNaker application kernel which reads pair of 32-bit integers from memory, adds them together, stores the result back into memory and exits.

Much of the code in this example is unchanged from the previous example so we will only discuss the changes.

The source files used in this tutorial can be downloaded below:

- Host program

- adder.py

- SpiNNaker kernel

- adder.c

- Makefile

#### Allocating SDRAM from the host

In our application, as in most real world applications, we'll use the on-chip SDRAM (shared between all cores on a chip) to load our two integers and store the result. By convention, the host program is responsible for allocating space in SDRAM.

The Rig *MachineController* class provides an *sdram\_alloc()* method which we'll use to allocate 12 bytes of SDRAM on a SpiNNaker chip. In this example we'll allocate some SDRAM on chip (0, 0). The first 8 bytes will contain the two numbers to be summed and will be written by our host program. The last four bytes will be written by the SpiNNaker application kernel and will contain the resulting sum.

```

sdram_addr = mc.sdram_alloc(12, x=0, y=0, tag=1)

```

The  $sdram_alloc()$  method returns the address of a block of SDRAM on chip (0, 0) which was allocated.

We also need to somehow inform the SpiNNaker application kernel of this address. To do this we can use the 'tag' argument to identify the allocated memory block. Later, once the application kernel has been loaded it can use sark\_tag\_ptr() to discover the address of tagged SDRAM blocks. In most applications, memory used by an application running on core 1 is given tag 1, memory for core 2 is given tag 2 and so on. Since an application kernel can discover the core number it is running on using spinl\_get\_core\_id(), the following line gets a pointer to the SDRAM block allocated for a particular core's application.

uint32\_t \*numbers = sark\_tag\_ptr(spin1\_get\_core\_id(), 0);

Note: Tags are assigned for a single SpiNNaker chip: tag numbers can be re-used on other chips.

#### Writing SDRAM from the host

After allocating our block of SDRAM we must populate it with the numbers to be added together. In this example, we pick two random numbers and, using Python's struct module, pack them into 8 bytes.

```

num_a = random.getrandbits(30)

num_b = random.getrandbits(30)

data = struct.pack("<II", num_a, num_b)</pre>

```

**Note:** The '<' prefix *must* be included in the struct format string to indicate that the data should be arranged in the little-endian order used by SpiNNaker.

The write() method of the MachineController is then used to write this value into the first 8 bytes of the SDRAM block we allocated.

mc.write(sdram\_addr, data, x=0, y=0)

**Warning:** The *write()* method will attempt to perform any write you specify. Due caution should be used to avoid data corruption or illegal memory accesses.

#### **Running the application kernel**

With the SDRAM allocated, tagged and populated with data, we can load our application kernel as in the previous example using *load\_application()*.

The application kernel adds together the numbers at the memory address discovered by sark\_tag\_ptr(), writes the result into memory and exits:

numbers[2] = numbers[0] + numbers[1];

**Note:** Although SDRAM *can* be accessed directly like this, 'real' application kernels often use DMA requests to avoid blocking on slow memory access.

#### Reading and writing SDRAM from the host

After waiting for the application kernel to exit, the host can read the answer back using *read()* and unpack it using Python's struct module.

```

result_data = mc.read(sdram_addr + 8, 4, x=0, y=0)

result, = struct.unpack("<I", result_data)

print("{} + {} = {}".format(num_a, num_b, result))</pre>

```

As before, the last step is to send a "stop" signal to SpiNNaker using *send\_signal()*. This signal will automatically free all allocated blocks of SDRAM.

In this tutorial we used some fairly low-level APIs for accessing SpiNNaker's memory. In the next tutorial we'll use some of Rig's higher-level APIs to make the process of accessing SpiNNaker's memory and cleaning up after an application easier and safer. Continue to *part 03*.

# 1.2.4 03: Reading and Writing SDRAM - Improved

We're now going to re-write the host-program from our previous example program, which used SpiNNaker to add two numbers together. In particular, some higher-level facilities of the *MachineController* will be used to make the host application simpler and more robust. The SpiNNaker application kernel, however, will remain unchanged.

The source files used in this tutorial can be downloaded below:

- Host program

- adder\_improved.py

- SpiNNaker kernel (unchanged from part 02)

- adder.c

- Makefile

#### **Reliably stopping applications**

Now that we're starting to allocate machine resources and write more complex programs it is important to be sure that the stop signal is sent to the machine at the end of our host application's execution. Rather than inserting a call to send\_signal() into every exit code path, Rig provides the application() context manager which automatically sends a stop signal when the block ends:

with mc.application():

# ...Application code...

When execution leaves an *application()* block, whether by reaching the end of the block, returning early from the function which contains it or encountering an exception, the stop signal is sent automatically.

In our new host program, we surround our application logic with an *application()* block. The *boot()* command is purposely placed outside the block since if the boot process fails, it is neither necessary nor possible to send a stop signal.

#### File-like memory access

When working with SDRAM it can be easy to accidentally access memory outside the range of an allocated buffer. To provide safer and more convenient access to SDRAM the *sdram\_alloc\_as\_filelike()* method produces a file-like *MemoryIO* object for the allocated memory. This object can be used just like a conventional file, for example using *read()*, *write()* and *seek()* methods. All writes and reads to the file are automatically constrained to the allocated block of SDRAM preventing accidental corruption of memory. Additionally, users of an allocated block of memory need not know anything about the chip or address of the memory and may even be oblivious to the fact that they're using anything other than a normal file. This can simplify application code by avoiding the need to pass around additional information.

We replace the previous calls to *sdram\_alloc()*, *write()* and *read()* with:

```

sdram = mc.sdram_alloc_as_filelike(12, x=0, y=0, tag=1)

sdram.write(data)

result_data = sdram.read(4)

```

Just like files, reads and writes occur immediately after the data the previous read and write encountered. seek() must be used move the 'read head' to other locations in memory. Note that in this case since the result value is written immediately after the two input values we do not need to seek before reading.

In the next part of the tutorial we'll use what we've learnt to take our first steps towards building a real application: a digital circuit simulator. Onward to *part 04*!

# 1.2.5 04: Circuit Simulation Proof-of-Concept

In this part of the tutorial we'll finally begin work on a real program: a digital circuit simulator. In this stage of the tutorial we'll build the SpiNNaker application kernels and a proof-of-concept host program to hook these kernels together in a fixed circuit to demonstrate everything working.

The source files used in this tutorial can be downloaded below:

- Host program

- circuit\_simulator\_proof.py

- SpiNNaker kernels

- gate.c

- stimulus.c

- probe.c

- Makefile

#### **Digital circuit simulation**

In this tutorial we'll build a digital circuit simulator which (rather inefficiently) simulates the behaviour of a circuit made up of simple logic gates all wired together.

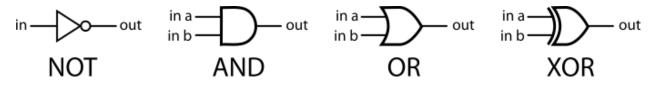

In our simulator, a logic gate is a device with one or two binary inputs and one binary output. In the picture below, four example logic gates are given along with truth-tables defining their behaviour.

Four simple 'logic gates' which each compute a simple boolean function. The 'truth tables' below enumerate the output values of each gate for every possible input.

NOT

| in | out |

|----|-----|

| 0  | 1   |

| 1  | 0   |

#### AND, OR and XOR

| in a | in b | out |    |     |

|------|------|-----|----|-----|

|      |      | AND | OR | XOR |

| 0    | 0    | 0   | 0  | 0   |

| 0    | 1    | 0   | 1  | 1   |

| 1    | 0    | 0   | 1  | 1   |

| 1    | 1    | 1   | 1  | 0   |

Though on their own these logic gates don't do anything especially interesting by combining them into circuits more interesting behaviour can be achieved. Indeed, computer processors are little more than a carefully chosen collection of logic gates!

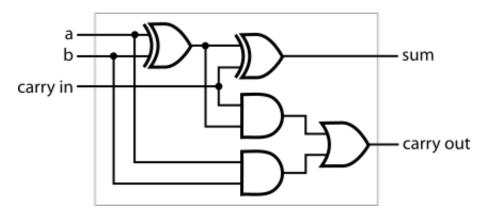

As an example, the circuit below is known as a 'full adder' which takes three one-bit binary numbers, 'a', 'b' and 'carry in' and adds them together to give a two-bit result whose least significant bit is 'sum' and whose most significant bit is 'carry out'.

For example if we set 'a' and 'carry in' to 1 and set 'b' to 0, the full-adder circuit will produce a 0 on its 'sum' output and a 1 on its 'carry out' output. Our inputs here are asking the full adder to compute "1 + 0 + 1" to which it dutifully answers "10" ("2" in binary).

Try following how the input values in this example flow through the full adder to produce the outputs in this example. For this tutorial it is not important to understand *why* the adder circuit works but you should be able to understand how input values flow through the circuit eventually resulting in outputs. Working out how to build a functioning CPU out of these gates is left as an exercise for the easily distracted reader and is well outside the scope of this tutorial...

#### Modelling a logic gate

Our circuit simulator will use a whole SpiNNaker core for each logic gate it simulates. Every millisecond each application core will recompute its output and send a multicast packet to any connected gates. When a gate receives a multicast packet indicating the value of one of its inputs it stores it to use next time the gate's output value is computed.

Rather than writing an individual SpiNNaker application kernel for each type of gate we want to simulate, we'll instead write a single application kernel which is configured with a look-up table (i.e. a 'truth table') by the host to whatever any functions we require.

gate.c contains the full source listing for our gate kernel. We'll walk through the key parts below.

```

void on_tick(uint32_t ticks, uint32_t arg1) {

// Terminate after the specified number of ticks.

// NB: the tick count starts from 1!

```

```

if (ticks > config->sim_length) {

spin1_exit(0);

return;

}

// Look-up the new output value

uint32_t lut_bit_number = last_input_a | (last_input_b << 1);

uint32_t output = (config->lut >> lut_bit_number) & 1;

// Send the output value of the simulated gate as the payload in a

// multicast packet.

spin1_send_mc_packet(config->output_key, output, WITH_PAYLOAD);

```

The timer is configured to call the on\_tick() function every millisecond. This function looks-up the desired output value in a lookup table based on the most recently received input values. The output value is then sent via a SpiNNaker multicast packet. The function is also responsible for terminating the simulation after a predetermined amount of time.

The last\_input\_a and last\_input\_b variables are set by the on\_mc\_packet() function which is called whenever a multicast packet arrives at the core.

```

void on_mc_packet(uint32_t key, uint32_t payload) {

if (key == config->input_a_key)

last_input_a = payload;

if (key == config->input_b_key)

last_input_b = payload;

}

```

}

This function simply checks to see which input the incoming multicast packet is related to by checking its key against the expected key for each of the two inputs.

The config struct used by the two callback functions above is expected to be written by the host and contains several fields describing the desired behaviour of the gate being simulated.

```

typedef struct {

// The number of milliseconds to run for

uint32_t sim_length;

// The routing key used by multicast packets relating to input a

uint32_t input_a_key;

// The routing key used by multicast packets relating to input b

uint32_t input_b_key;

// The routing key to use when transmitting the output value

uint32_t output_key;

// A lookup table from input a and b to output value.

// input a input b lut bit number

// ======

_____ ___ ____

// 0

0

0

// 1

0

1

// 0

1

2

// 1

1

3

// ====== ======

_____

```

```

uint32_t lut;

} config_t;

config_t *config;

```

The pointer to the config struct is set using the  $sark_tag_ptr()$  as described in the previous tutorials and the callbacks setup in the  $c_main()$  function.

#### Stimulus and probing kernels

To make our simulator useful we need to be able to provide input stimulus and record the output produced. To do this we'll create two additional SpiNNaker application kernels: stimulus.c and probe.c.

The stimulus kernel will simply output a sequence of values stored in memory, one each millisecond. As in the gate kernel, a configuration struct is defined which the host is expected to populate:

```

typedef struct {

// The number of milliseconds to run for

uint32_t sim_length;

// The routing key to use when transmitting the output value

uint32_t output_key;

// An array of ceil(sim_length/8) bytes where bit-0 of byte[0] contains the_

·/ bit to send, bit-1 gives the second bit and bit-0 of byte[1] gives the

// eighth bit and so on...

uint8_t stimulus[];

} config_t;

```

This configuration is then used by the timer interrupt to send output values into the network:

```

void on_tick(uint32_t ticks, uint32_t arg1) {

// The tick count provided by Spin1 API starts from 1 so decrement to get a

// 0-indexed count.

ticks--;

// Terminate after the specified number of ticks.

if (ticks >= config->sim_length) {

spin1_exit(0);

return;

}

// Get the next output value

uint32_t output = (config->stimulus[ticks / 8] >> (ticks % 8)) & 1;

// Send the new output value as the payload in a multicast packet.

spin1_send_mc_packet(config->output_key, output, WITH_PAYLOAD);

}

```

The probe kernel takes on the reverse role: every millisecond it records into memory the most recent input value it received. The host can later read this data back. Once more, a configuration struct is defined which the host will populate and to which the probe will add recorded data:

```

typedef struct {

// The number of milliseconds to run for

uint32_t sim_length;

// The routing key used by multicast packets relating to the probed input

uint32_t input_key;

// An array of ceil(sim_length/8) bytes where bit-0 of byte[0] will be

// written with value in the first millisecond, bit-1 gives the value in the

// second millisecond and bit-0 of byte[1] gives the value in the eighth

// millisecond and so on...

uchar recording[];

} config_t;

```

The 'recording' array is zeroed during kernel startup to save the host from having to write the zeroes over the network:

The array is then written to once per millisecond with the most recently received value:

```

void on_tick(uint32_t ticks, uint32_t argl) {

// The tick count provided by Spin1 API starts from 1 so decrement to get a

// 0-indexed count.

ticks--;

// Terminate after the specified number of ticks.

if (ticks >= config->sim_length) {

spin1_exit(0);

return;

}

// Pause for a while to allow values sent during this millisecond to arrive

// at this core.

spin1_delay_us(700);

// Record the most recently received value into memory

config->recording[ticks/8] |= last_input << (ticks % 8);

}</pre>

```

As in the gate kernel, a callback on multicast packet arrival keeps track of the most recently received input value:

```

void on_mc_packet(uint32_t key, uint32_t payload) {

if (key == config->input_key)

last_input = payload;

}

```

#### Compiling the kernels

A Makefile is provided which builds all three kernels when you type:

\$ make

#### A proof-of-concept host program

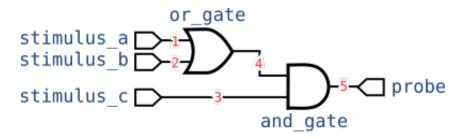

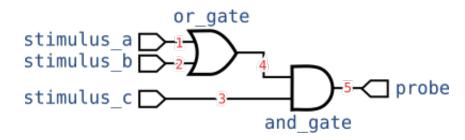

To try out our new application kernels we'll now put together a proof-of-concept host application which uses our kernels to simulate a single circuit and hard-codes all configuration data for each application kernel. Our proof-of-concept system will simulate the following circuit:

To do this we'll need 6 SpiNNaker cores (one for each gate, probe and stimulus). We'll arbitrarily use the following assignment of cores:

| Component  | Chip   | Core | Kernel   |

|------------|--------|------|----------|

| stimulus_a | (0, 0) | 1    | stimulus |

| stimulus_b | (0, 0) | 2    | stimulus |

| stimulus_c | (0, 0) | 3    | stimulus |

| or_gate    | (1, 0) | 1    | gate     |

| and_gate   | (1,0)  | 2    | gate     |

| probe      | (1, 1) | 1    | probe    |

The five wires numbered 1 to 5 in the circuit diagram will be carried by multicast routes whose key is the wire number. This assignment is illustrated in the figure below:

**Note:** Core 0 every SpiNNaker chip (not shown in the figure above) is always used by the 'monitor process' (SC&MP) which is used to facilitate control of the system. It cannot be used to run SpiNNaker application kernels.

We'll run our simulation for 64 ms and configure each stimulus kernel such that each of the 8 combinations of stimulus value are held for 8 ms each to allow time for the signals to propagate through the circuit.

The proof-of-concept host program is provided in full in circuit\_simulator\_proof.py and we'll walk through the key steps below. After creating a *MachineController* instance and booting the machine as usual, the first step is to allocate memory for the configuration structs of each of the six applications using *sdram\_alloc\_as\_filelike()*:

```

with mc.application():

# Allocate a tagged block of SDRAM to hold the configuration struct for

# each application kernel.

with mc(x=0, y=0):

# Space for sim_length, output_key and space for 64 ms of stimulus

# data.

stimulus_a_config = mc.sdram_alloc_as_filelike(4 + 4 + 8, tag=1)

stimulus_b_config = mc.sdram_alloc_as_filelike(4 + 4 + 8, tag=2)

stimulus_c_config = mc.sdram_alloc_as_filelike(4 + 4 + 8, tag=3)

with mc(x=1, y=0):

# Space for all 5 uint32_t values in the config struct

or_gate_config = mc.sdram_alloc_as_filelike(5 * 4, tag=1)

and_gate_config = mc.sdram_alloc_as_filelike(5 * 4, tag=2)

# Space for sim_length, input_key and space for 64 ms of stimulus data.

probe_config = mc.sdram_alloc_as_filelike(4 + 4 + 8, x=1, y=1, tag=1)

```

**Tip:** In the code above, *MachineController* is used as a context manager. This allows a common set of arguments to be specified once, the chip coordinate arguments in this example, and omitted in subsequent calls.

Next we write the configuration structs using Python's struct module and the bitarray package to pack the desired data:

```

# The stimulus data (tries every combination of a, b and c for 8 ms each)

#

1

1

1

1

1

1

1

# Write stimulus configuration structs

stimulus_a_config.write(struct.pack("<II", 64, 0x0000001))</pre>

stimulus_a_config.write(bitarray(stim_a, endian="little").tobytes())

stimulus_b_config.write(struct.pack("<II", 64, 0x0000002))</pre>

stimulus_b_config.write(bitarray(stim_b, endian="little").tobytes())

stimulus_c_config.write(struct.pack("<II", 64, 0x0000003))</pre>

stimulus_c_config.write(bitarray(stim_c, endian="little").tobytes())

# Write gate configuration structs, setting the look-up-tables to implement

# the two gates' respective functions.

or_gate_config.write(struct.pack("<51",

```

|                                 | 64,                                                     | # sim_length                |

|---------------------------------|---------------------------------------------------------|-----------------------------|

|                                 | 0x00000001,                                             | <pre># input_a_key</pre>    |

|                                 | 0x0000002,                                              | # input_b_key               |

|                                 | 0x0000004,                                              | # output_key                |

|                                 | 0b1110))                                                | # lut (OR)                  |

| and_gate_config.write(struct.pa | ack("<5I",                                              |                             |

|                                 | 64,                                                     | # sim_length                |

|                                 | 0x0000004,                                              | <pre># input_a_key</pre>    |

|                                 | 0x0000003,                                              | # input_b_key               |

|                                 | 0x00000005,                                             | # output_key                |

|                                 | 0b1000))                                                | # lut (AND)                 |

|                                 |                                                         |                             |

| # Write the probe's configurat. | ion struct (not                                         | e this doesn't write to the |

| # buffer used to store recorded | d values).                                              |                             |

| probe config.write(struct.pack  | (" <tt", 0x0<="" 64,="" td=""><td>0000005))</td></tt",> | 0000005))                   |

In order to route the multicast packets to their appropriate destinations we must define some routing table entries on the chips we're using. We build up a dictionary which contains a list of *RoutingTableEntry* tuples for each SpiNNaker chip where routing table entries must be added. A *RoutingTableEntry* tuple corresponds directly to a SpiNNaker routing table entry which routes packets to the supplied set of *Routes* when they match the supplied key and mask value.

The routing tables described are finally loaded onto their respective chips using the <code>load\_routing\_tables()</code> method of the <code>MachineController</code>.

**Note:** The details of SpiNNaker's multicast router are outside of the scope of this tutorial. In the next part of the tutorial we'll use Rig's place-and-route facilities to generate these tables automatically so understanding how SpiNNaker's router works is not strictly necessary (though often helpful!).

In brief: we must add a routing entry wherever a packet enters the network, changes direction or leaves the network for a local core. A packet's routing key is matched by an entry in the table whenever (packet\_key & table\_entry\_mask) == table\_entry\_key. If no routing entry matches a packet's key, the packet is 'default-routed' in a straight line to the opposite link to the one it arrived on. The Section 10.4 (page 39) of the SpiNNaker Datasheet provides a good introduction to SpiNNaker's multicast router and routing tables.

```

# Define routing tables for each chip

routing_tables = \{(0, 0): [],

(1, 0): [],

(1, 1): [] \}

# Wire 1

routing_tables[(0, 0)].append(

RoutingTableEntry({Routes.east}, 0x0000001, 0xFFFFFFF))

routing_tables[(1, 0)].append(

RoutingTableEntry({Routes.core_1}, 0x0000001, 0xFFFFFFF))

# Wire 2

routing_tables[(0, 0)].append(

RoutingTableEntry({Routes.east}, 0x0000002, 0xFFFFFFF))

routing_tables[(1, 0)].append(

RoutingTableEntry({Routes.core_1}, 0x0000002, 0xFFFFFFF))

# Wire 3

routing_tables[(0, 0)].append(

```

```

RoutingTableEntry({Routes.east}, 0x0000003, 0xFFFFFFF))

routing_tables[(1, 0)].append(

RoutingTableEntry({Routes.core_2}, 0x0000003, 0xFFFFFFF))

# Wire 4

routing_tables[(1, 0)].append(

RoutingTableEntry({Routes.core_2}, 0x0000004, 0xFFFFFFFF))

# Wire 5

routing_tables[(1, 0)].append(

RoutingTableEntry({Routes.north}, 0x0000005, 0xFFFFFFFF))

routing_tables[(1, 1)].append(

RoutingTableEntry({Routes.core_1}, 0x0000005, 0xFFFFFFFF))

# Allocate and load the above routing entries onto their respective chips

mc.load routing tables(routing tables)

```

We're finally ready to load our application kernels onto their respective chips and cores using load\_application():

```

mc.load_application({

"stimulus.aplx": {(0, 0): {1, 2, 3}},

"gate.aplx": {(1, 0): {1, 2}},

"probe.aplx": {(1, 1): {1}},

})

```

**Note:** *load\_application()* uses an efficient flood-fill mechanism to applications onto several chips and cores simultaneously.

The 'Spin1 API' used to write the application kernels causes our kernels to wait at the 'sync0' barrier once the spin1\_start() function is called at the end of c\_main(). We will use wait\_for\_cores\_to\_reach\_state() to wait for all six application kernels to reach the 'sync0' barrier:

```

mc.wait_for_cores_to_reach_state("sync0", 6)

```

Next we send the 'sync0' signal using send\_signal(). This starts our application kernels running. After 64 ms all of the applications should terminate and we wait for them to exit using wait\_for\_cores\_to\_reach\_state().

```

mc.send_signal("sync0")

time.sleep(0.064)  # 64 ms

mc.wait_for_cores_to_reach_state("exit", 6)

```

Next we retrieve the result data recorded by the probe:

```

probe_recording = bitarray(endian="little")

probe_recording.frombytes(probe_config.read(8))

```

Note: Note that the probe\_config file-like object's read pointer was moved to the start of the recording array when the configuration data before it was written earlier in the host program.

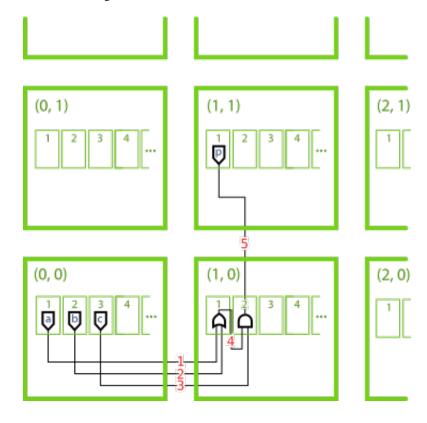

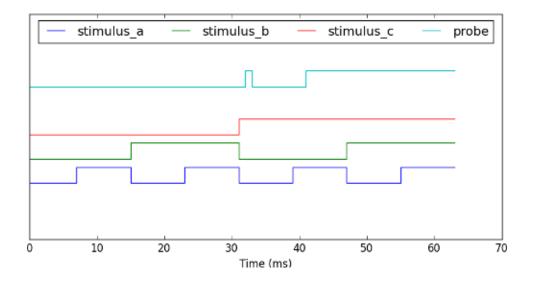

The stimulus and recorded data are plotted using pyplot to produce a figure like the one below:

**Note:** The recording shows a 'glitch' at time=32 which is caused by propagation delays in our circuit rather than a bug in our simulator. In fact, our simulator has accurately modelled an unintended feature of our circuit!

And there we have it: a real digital circuit simulation running on SpiNNaker! Unfortunately, our simulator is not especially flexible. Changing the circuit requires re-writing swathes of code and hand-generating yet more routing tables. In the next part of the tutorial we'll make use of the automatic place-and-route features included in the Rig library to take care of this for us. So without further delay, let's proceed to *part 05*!

# 1.2.6 05: Circuit Simulation

In the *previous part of this tutorial* we built a simple digital circuit simulator using several application kernels running on multiple SpiNNaker chips which communicated with multicast packets. In our proof-of-concept host program, the chip and core to use for each kernel was chosen by hand and all routing tables were written manually. Though this works, it made our simulator incredibly inflexible and the host program hard to modify and extend.

In this part of the tutorial we'll leave the application kernels unchanged but re-write our host program to make use of the automatic place-and-route tools provided by Rig. These tools automate the process of assigning application kernels to specific cores and generating routing tables while attempting to make efficient use of the machine. We'll also restructure our host program to be more like a real-world application complete with a simple user-facing interface.

The source files used in this tutorial can be downloaded below:

- Host program

- circuit\_simulator.py

- Example circuit simulation script

- example\_circuit.py

- SpiNNaker kernels (unchanged from part 04)

- gate.c

- stimulus.c

- probe.c

- Makefile

#### Defining the circuit simulator user interface/API

If our circuit simulator is to be useful it must present a sensible API to allow users to describe their circuits. In this example we'll implement an API which looks like this:

```

import sys

from circuit_simulator import Simulator, Stimulus, Or, And, Probe

# Define a 64 ms simulation to be run on the given SpiNNaker machine

sim = Simulator(sys.argv[1], 64)

# Define three stimulus generators which together produce all 8 combinations of

# values.

stimulus_a = Stimulus(

stimulus_b = Stimulus(

stimulus_c = Stimulus(

# Define the two gates

or_gate = Or(sim)

and_gate = And(sim)

# Define a probe to record the output of the circuit

probe = Probe(sim)

# Wire everything together

or_gate.connect_input("a", stimulus_a.output)

or_gate.connect_input("b", stimulus_b.output)

and_gate.connect_input("a", stimulus_c.output)

and_gate.connect_input("b", or_gate.output)

probe.connect_input(and_gate.output)

# Run the simulation

sim.run()

# Print the results

print("Stimulus A: " + stimulus_a.stimulus)

print("Stimulus B: " + stimulus_b.stimulus)

print("Stimulus C: " + stimulus_c.stimulus)

" + probe.recorded_data)

print("Probe:

```

This script defines the same circuit which we hard-coded in *part 04*:

With our desired API in mind, lets design our circuit simulator!

#### Place and Route using Rig

Before diving into the code it is first important to understand what the Rig place-and-route tools do.

Rig provides a suite of placement and routing algorithms in its *rig.place\_and\_route* module. In essence, these algorithms accept abstract descriptions of graphs of communicating SpiNNaker application kernels as input. Based on this information the place and route algorithms select which core each kernel will be loaded onto, keeping communicating cores close together to reduce network load. In addition, routing tables which make efficient use of SpiNNaker's network are generated.

In Rig terminology, the abstract (hyper-)graph of application kernels are known as *vertices* which are connected together by *nets*:

- **vertices** Approximately speaking, a vertex represents a group of cores and SDRAM which must be assigned in one piece to a chip somewhere. In our circuit simulator, a vertex represents a single gate, stimulus or probe and each requires a single core and some quantity of SDRAM.

- **nets** A net typically represents a 1-to-many flow of multicast packets between vertices. A net has a single *source* vertex and many *sink* vertices. In our circuit simulator, a net corresponds to a wire in our circuit, where the source is the gate or stimulus output driving the wire and the sinks are the connected gate and probe inputs.

In addition to graph of vertices and nets, the place and route tools require a description of the SpiNNaker machine our simulation will be running on. As we will see later, the *MachineController* provides a method for gathering this information.

#### **Building the circuit simulator API**

What follows is a (non-linear) walk-through of the most important parts of the circuit simulator host program provided in circuit\_simulator.py.

In most host applications built with Rig, the graph of vertices and nets fed to the place and route tools are generated from application-specific data structures shortly before performing the place-and-route. This allows the majority of the application to use data structures which best fit the application. In this circuit simulator example we'll follow this approach too, so let's start by defining the Python classes which make up the API.

#### Defining a wire

A wire represents a connection from one the output of one component to the inputs of many other components and is defined as follows:

```

routing_key : int

"""

self.source = source

self.sinks = sinks

self.routing_key = routing_key

```

A \_Wire instance contains a source component, a list of sink components and a unique routing key to use in the simulation. The Simulator object (to be defined later) will be responsible for creating new \_Wire objects.

#### Defining components (gates, stimuli and probes)

At the heart of our circuit simulator is our two-input, one-output, lookup-table-based logic gate so let's define our Gate component first like so:

```

class Gate (object):

"""A 2-input 1-output logic gate implemented using a lookup-table."""

def __init__(self, simulator, lookup_table):

"""Define a new gate.

Parameters

simulator : :py:class:`.Simulator`

The simulator which will be responsible for simulating this gate.

lookup_table : int

A lookup table giving the output value of the gate as a 4-bit

number where each bit gives the output for a particular combination

of input values.

_____ __ ____ ____

input a input b lut bit number

_____ ____ ____

0

0

0

0

1

1

0

1

2

7

1

3

_____

.....

self._simulator = simulator

self._lookup_table = lookup_table

# Register this component with the simulator

self._simulator._add_component(self)

# The two inputs, initially not connected

self._inputs = {"a": None, "b": None}

# A new wire will be created and sourced by this gate

self.output = self._simulator._new_wire(self)

def connect_input(self, name, wire):

"""Connect the specified input to a wire."""

self._inputs[name] = wire

wire.sinks.append(self)

```

In the constructor we simply store a reference to the Simulator object along with a copy of the lookup table pro-

vided. We also inform the Simulator of the existance of the component using Simulator.\_add\_component. The \_inputs attribute will hold references to the \_Wires connected to each input and the output attribute holds a reference to (a newly created) \_Wire which will be driven by the gate.

The Gate.connect\_input method connects a \_Wire to an input by storing a reference to the \_Wire object and adding the component to the \_Wire's list of sinks.

We also define various subclasses of Gate which, for the sake of convenience, simply define the lookup table to be used. For example an AND-gate component is defined like so:

```

class And(Gate):

"""An AND gate."""

def __init__(self, simulator):

super(And, self).__init__(simulator, 0b1000)

```

The Probe object is defined in a similar way to the Gate but doesn't define an output:

```

class Probe (object):

"""A 1-bit recording probe."""

def __init__(self, simulator):

"""Define a new probe.

Parameters

simulator : :py:class:`.Simulator`

The simulator in which the probe will be used.

.....

self._simulator = simulator

self.recorded_data = None

# Register this component with the simulator

self._simulator._add_component(self)

# The input, initially disconnected

self._input = None

def connect_input(self, wire):

"""Probe the specified wire."""

self._input = wire

wire.sinks.append(self)

```

Finally, the Stimulus object is defined but, since it doesn't have any inputs, the connect\_input method is excluded:

```

class Stimulus(object):

"""A 1-bit stimulus source."""

def __init__(self, simulator, stimulus=""):

"""Define a new stimulus source.

Parameters

-------

simulator : :py:class:`.Simulator`

The simulator in which the stimulus will be used.

stimulus : str

A string of "0" and "1"s giving the stimulus to generate for each

```

```

millisecond in the simulation. Will be zero-padded or truncated to

match the length of the simulation.

"""

self._simulator = simulator

self.stimulus = stimulus

# Register this component with the simulator

self._simulator._add_component(self)

# A new wire will be created sourced by this stimulus generator

self.output = self._simulator._new_wire(self)

```

#### Defining the simulator

All that remains to be defined of our API is the Simulator object. The Simulator simply stores the hostname and simulation length provided and maintains lists of components and wires which have been added to the simulation:

```

class Simulator(object):

"""A SpiNNaker-based digital logic simulator."""

def __init__(self, hostname, length):

""Create a new simulation.

Parameters

hostname : str

The hostname or IP of the SpiNNaker machine to use.

length : int

The number of milliseconds to run the simulation for.

.....

self._hostname = hostname

self.length = length

# A list of components added to the simulation

self._components = []

# A list of wires used in the simulation

self._wires = []

def _add_component(self, component):

"""Add a component to the simulation.

Called internally by components on construction.

.....

self._components.append(component)

def _new_wire(self, source, sinks=None):

"""Create a new :py:class:`._Wire` with a unique routing key."""

# Assign sequential routing key to new nets.

wire = _Wire(source, sinks if sinks is not None else [], len(self._wires))

self._wires.append(wire)

return wire

```

#### Making it work

At this point, our API is complete with the notable exception of the Simulation.run() method. At a high level, the run() method performs the following steps:

- Build a graph of the form accepted by Rig's place and route tools.

- Perform place and route.

- Load the configuration data, routing tables and application kernels required.

- Run the simulation.

- Read back results captured by probes.

We'll now proceed to break down this function and look at its operation in detail.

#### Building a place-and-routeable graph

To perform place and route we must build a graph describing our simulation in the format required by Rig.

The first thing we need to do is define the resources required by each vertex in the graph. Rig allows us to use any Python <code>object</code> to represent a vertex and since each component in our simulation will become a vertex in our graph we'll use the <code>objects</code> we defined above to identify the vertices. We build a <code>vertices\_resources</code> dictionary which enumerates the resources consumed by each vertex in our application:

```

vertices_resources = {

# Every component runs on exactly one core and consumes a certain

# amount of SDRAM to hold configuration data.

component: {Cores: 1, SDRAM: component._get_config_size()}

for component in self._components

}

```

Each entry in the vertices\_resources dictionary contains another dictionary mapping 'resources' to the required quantities of each resource. As in most applications, the only resources we care about are Cores and SDRAM. By convention these resources are identified to by the corresponding *Cores* and *SDRAM* sentinels defined by Rig.

Each vertex requires exactly one core but the amount of SDRAM required depends on the type of component and length of the simulation. A  $_get_config_size()$  method is added to each of our component types to compute their SDRAM requirements:

```

class Gate(object):

def _get_config_size(self):

"""Get the size of configuration block needed for this gate."""

# The config contains 5x uint32_t

return 5 * 4

```

```

class Probe(object):

def _get_config_size(self):

"""Get the size of configuration block needed for this probe."""

# The config contains 2x uint32_t and a byte for every 8 bits of

# recorded data.

return (2 * 4) + ((self._simulator.length + 7) // 8)

```

```

class Stimulus(object):

def _get_config_size(self):

"""Get the size of configuration block needed for this stimulus."""

# The config contains 2x uint32_t and a byte for every 8 bits of

```

```

# stimulus data.

return (2 * 4) + ((self._simulator.length + 7) // 8)

```

Next we must also define the filename of the spinnaker application kernel (i.e. the APLX file) used for each vertex.

Once again we support this by adding a \_get\_kernel() method to each component type:

```

class Gate(object):

def _get_kernel(self):

""""Get the filename of the SpiNNaker application kernel to use."""

return "gate.aplx"

```

```

class Probe(object):

def _get_kernel(self):

"""Get the filename of the SpiNNaker application kernel to use."""

return "probe.aplx"

```

```

class Stimulus(object):

def _get_kernel(self):

"""Get the filename of the SpiNNaker application kernel to use."""

return "stimulus.aplx"

```

Next, we enumerate the nets representing the streams of multicast packets flowing between vertices, as well as the routing keys and masks used for each net. Rig expects nets to be defined by *Net* objects. Like the \_Wire objects in our simulator, *Nets* simply contain a source vertex and a list of sink vertices. In the code below we build a dict mapping *Nets* to (key, mask) tuples for each wire in the simulation:

The final piece of information required is a description of the SpiNNaker machine onto which our application will be placed and routed. Using a *MachineController* we first *boot()* the machine and then interrogate it using *get\_system\_info()* which returns a SystemInfo object. This object contains a detailed description of the machine, for example, enumerating working cores and links. This description will be used shortly to perform place and route.

```

mc = MachineController(self._hostname)

mc.boot()

system_info = mc.get_system_info()

```

#### **Place and route**

The place and route process can be broken up into many steps such as placement, allocation, routing and routing table generation. Though some advanced applications may find it useful to break these steps apart, our circuit simulator, like many other applications, does not. Rig provides a *place\_and\_route\_wrapper()* function which saves us from the 'boilerplate' of doing each step separately. This function takes the graph description we constructed above and performs the place and route process in its entirety.

The placements and allocations dict returned by *place\_and\_route\_wrapper()* together define the specific chip and core each vertex has been assigned to (see *place()* and *allocate()* for details).

application\_map is a dict describing what application kernels need to be loaded onto what cores in the machine.

Finally, routing\_tables contains a dict giving the routing tables to be loaded onto each core in the machine.

#### Loading and running the simulation

We are now ready to load and execute our circuit simulation on SpiNNaker. The first step is to allocate blocks of SDRAM containing configuration data on every chip where our application kernels will run.

The *sdram\_alloc\_for\_vertices()* utility function takes a *MachineController* and the placements and allocations dicts produced during place and route and allocates a block of SDRAM for each vertex. Each allocation is given a tag matching the core number of the vertex, and the size of the allocation is determined by the quantity of *SDRAM* consumed by the vertex, as originally indicated in vertices\_resources.

The dict returned is a mapping from each vertex (i.e. instances of our component classes) to a *MemoryIO* file-like interface to SpiNNaker's memory.

We add a \_write\_config method to each of our component classes which is passed a *MemoryIO* object into which configuration data is written.

```

for component, memory in memory_allocations.items():

component._write_config(memory)

```

The \_write\_config functions for each component type are as follows:

```

class Gate (object):

def _write_config(self, memory):

"""Write the configuration for this gate to memory."""

memory.seek(0)

memory.write(struct.pack("<51",</pre>

# sim_length

self._simulator.length,

# input_a_key

self._inputs["a"].routing_key

if self._inputs["a"] is not None

else OxFFFFFFFF,

# input_b_key

self._inputs["b"].routing_key

if self._inputs["b"] is not None

else OxFFFFFFFF,

# output_key

self.output.routing_key,

# lut

self._lookup_table))

```

Next, the routing tables and SpiNNaker applications are loaded using load\_routing\_tables() and load\_application():

```

# Load all routing tables

mc.load_routing_tables(routing_tables)

# Load all SpiNNaker application kernels

mc.load_application(application_map)

```

We now wait for the applications to reach their initial barrier, send the 'sync0' signal to start simulation and, finally, wait for the cores to exit.

```

# Wait for all six cores to reach the 'sync0' barrier

mc.wait_for_cores_to_reach_state("sync0", len(self._components))

# Send the 'sync0' signal to start execution and wait for the

# simulation to finish.

mc.send_signal("sync0")

time.sleep(self.length * 0.001)

mc.wait_for_cores_to_reach_state("exit", len(self._components))

```

The last step is to read back results from the machine. As with loading, we add a \_read\_results method to each component type which we call with a *MemoryIO* object from which it should read any results it requires:

```

for component, memory in memory_allocations.items():

component._read_results(memory)

```

The \_read\_results method is a no-op for all but the Probe component whose implementation is as follows:

#### Trying it out

Congratulations! Our circuit simulator is now complete! We can now run the example script we used to define our simulator's API and within a second or so we have our results!

# 1.3 Tutorial: Controlling SpiNNaker machines

SpiNNaker machines consist of a network of SpiNNaker chips and, in larger systems, a set of Board Management Processors (BMPs) which control and monitor systems' power and temperature. SpiNNaker (and BMPs) are controlled using SCP packets (a protocol built on top of SDP) sent over the network to a machine. Rig includes a set of high-level wrappers around the low-level SCP commands which are tailored towards SpiNNaker application developers.

**Note:** Rig does not aim to provide a complete Python implementation of the full (low-level) SCP command set. Users who encounter missing functionality as a result of this are encouraged to submit a patch or open an issue as the developers are open to (reasonable) suggestions!

In addition to these high-level interfaces, Rig includes a lower-level interface for sending and receiving applicationdefined SDP and SCP packets to running applications via a socket.

The two high-level machine control interfaces are:

MachineController Interact with and control SpiNNaker chips, e.g. boot, load applications, read/write memory.

**BMPController** Interact with and control BMPs, e.g. control power-supplies, monitor system temperature, read/write FPGA registers. Only applicable to machines based on SpiNN-5 boards.

The low-level SDP and SCP interfaces are:

**SDPPacket** Pack and unpack SDP packets.

SCPPacket Pack and unpack SCP packets.

A tutorial for each of these interfaces is presented below.

## 1.3.1 MachineController

To get started, let's instantiate a *MachineController*. This is as simple as giving the hostname or IP address of the machine:

```

>>> from rig.machine_control import MachineController

>>> mc = MachineController("spinnaker_hostname")

```

**Note:** If you're using a multi-board machine, give the hostname of the (0, 0) chip. Support for connecting to multiple Ethernet ports of a SpiNNaker machine is not currently available but should be automatic.

## **Booting**

You can boot () the system like so:

```

>>> mc.boot()

True

```

If the machine could not be booted for any reason a *rig.machine\_control.machine\_controller*. *SpiNNakerBootError* will be raised. If no exception is raised, the machine is booted and ready to use. The return value of *boot()* indicates whether the machine was actually booted (True), or if it was already booted and thus nothing was done (False), most applications may consider the boot to be a success either way.

If you're using a SpiNN-2 or SpiNN-3 board booted without arguments, only LED 0 will be usable. To enable the other LEDs, instead boot the machine using one of the pre-defined boot option dictionaries in *rig.machine\_control. boot*, for example:

```

>>> from rig.machine_control.boot import spin3_boot_options

>>> mc.boot(**spin3_boot_options)

True

```

## **Probing for Available Resources**

The get\_system\_info() method returns a SystemInfo object describing which chips, links and cores are alive and also the SDRAM available:

>>> system\_info = mc.get\_system\_info()

This object can also be used to guide Rig's place and route utilities (see rig.place\_and\_route. place\_and\_route\_wrapper, rig.place\_and\_route.utils.build\_machine and rig. place\_and\_route.utils.build\_core\_constraints).

## **Loading Applications**

The *load\_application()* method will, unsurprisingly, load an application onto an arbitrary set of SpiNNaker cores. For example, the following code loads the specified APLX file to cores 1, 2 and 3 of chip (0, 0) and cores 10 and 11 of chip (0, 1):

```

>>> targets = {(0, 0): set([1, 2, 3]),

... (0, 1): set([10, 11])}

>>> mc.load_application("/path/to/app.aplx", targets)

```

Alternatively, this method accepts dictionaries mapping applications to targets, such as those produced by *rig. place\_and\_route\_wrapper*.

*load\_application()* verifies that all applications have been successfully loaded (re-attempting a small number of times if necessary). If not all applications could be loaded, a *SpiNNakerLoadingError* exception is raised.

Many applications require the *sync0* signal to be sent to start the application's event handler after loading. We can wait for all cores to reach the *sync0* barrier using wait\_for\_cores\_to\_reach\_state and then send the *sync0* signal using send\_signal:

```

>>> # In the example above we loaded 5 cores so we expect 5 cores to reach

>>> # sync0.

>>> mc.wait_for_cores_to_reach_state("sync0", 5)

5

>>> mc.send_signal("sync0")

```

Similarly, after application execution, the application can be killed with:

```

>>> mc.send_signal("stop")

```

Since the stop signal also cleans up allocated resources in a SpiNNaker machine (e.g. stray processes, routing entries and allocated SDRAM), it is desirable for this signal to reliably get sent even if something crashes in the host application. To facilitate this, you can use the *application()* context manager:

```

>>> with mc.application():

# Main application code goes here, e.g. loading applications,

# routing tables and SDRAM.

>>> # When the above block exits (even if due to an exception), the stop

>>> # signal will be sent to the application.

```

**Note:** Many application-oriented methods accept an *app\_id* argument which is given a sensible default value. If the *MachineController.application()* context manager is given an app ID as its argument, this app ID will become the default *app\_id* within the *with* block. See the section on context managers below for more details.

### Loading Routing Tables

Routing table entries can be loaded using *load\_routing\_tables* () like so:

```

>>> routing_tables = {

... (0, 0): [RoutingTableEntry(...), ...],

... (0, 1): [RoutingTableEntry(...), ...],

... ...

... }

>>> mc.load_routing_tables(routing_tables)

```

This command allocates and then loads the requested routing table entries onto each of the supplied chips. The supplied data structure matches that produced by rig.place\_and\_route.place\_and\_route\_wrapper().

#### Allocating/Writing/Reading SDRAM

Many SpiNNaker applications require the writing and reading of large blocks of SDRAM data. The recommended way of doing this is to allocate blocks of SDRAM using *sdram\_alloc()* with an identifying 'tag'. The The SpiNNaker application can later use this tag number to look up the address of the allocated block of SDRAM. Not only does this

avoid the need to explicitly communicate SDRAM locations to the application it also allows SARK to safely allocate memory in the SDRAM.

read() and write() methods are provided which can read and write arbitrarily large blocks of data to and from memory in SpiNNaker:

```

>>> # Allocate 1024 bytes of SDRAM with tag '3' on chip (0, 0)

>>> block_addr = mc.sdram_alloc(1024, 3, 0, 0)

>>> mc.write(block_addr, b"Hello, world!")

>>> mc.read(block_addr, 13)

b"Hello, world!"

```

Rig also provides a file-like I/O wrapper (*MemoryIO*) which may prove easier to integrate into applications and also ensures reads and writes are constrained to the allocated region.

```

>>> # Allocate 1024 bytes of SDRAM with tag '3' on chip (0, 0)

>>> block = mc.sdram_alloc_as_filelike(1024, 3, 0, 0)

>>> block.write(b"Hello, world!")

>>> block.seek(0)

>>> block.read(13)

b"Hello, world!"

```

File-like views of memory can also be sliced to allow a single allocation to be safely divided between different parts of the application:

```

>>> hello = block[0:5]

>>> hello.read()

b"Hello"

```

The *sdram\_alloc\_for\_vertices()* utility function is provided to allocate multiple SDRAM blocks simultaneously. This will be especially useful if you're using Rig's *place and route tools*, since the utility accepts the place-and-route tools' output format. For example:

```

>>> placements, allocations, application_map, routing_tables = \

... rig.place_and_route.wrapper(...)

>>> from rig.machine_control.utils import sdram_alloc_for_vertices

>>> vertex_memory = sdram_alloc_for_vertices(mc, placements, allocations)

>>> # The returned dictionary maps from vertex to file-like wrappers

>>> vertex_memory[vertex].write(b"Hello, world!")

```

### **Context Managers**

Many methods of *MachineController* require arguments such as *x*, *y*, *p* or *app\_id* which can quickly lead to repetitive and messy code. To reduce the repetition Python's with statement can be used:

```

>>> # Within the block, all commands will affect chip (1, 2)

>>> with mc(x = 1, y = 2):

... block_addr = mc.sdram_alloc(1024, 3)

... mc.write(block_addr, b"Hello, world!")

```

## 1.3.2 BMPController

A limited set of utilities are provided for interacting with SpiNNaker BMPs which are contained in the *BMPController* class. In systems with either a single SpiNN-5 board or a single frame of SpiNN-5 boards which

are connected via a backplane, the class can be constructed like so:

```

>>> from rig.machine_control import BMPController

>>> bc = BMPController("bmp_hostname")

```

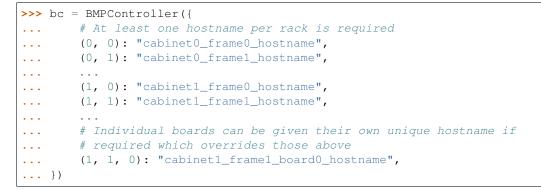

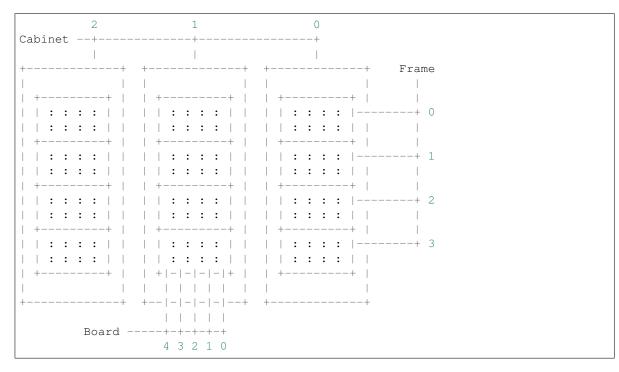

For larger systems which contain many frames of SpiNNaker boards, at least one IP address or hostname must be specified for each:

Boards are referred to by their (cabinet, frame, board) coordinates:

| 2        | 1                                    | 0            |  |

|----------|--------------------------------------|--------------|--|

| _        | -                                    |              |  |

| Cabinet+ |                                      |              |  |

|          |                                      |              |  |

| ++       | ++                                   | ++ Frame     |  |

|          |                                      |              |  |

|          |                                      |              |  |

| ++       | ++                                   | ++           |  |

|          | : : : :                              | : : :   + 0  |  |

|          |                                      |              |  |

|          | ++                                   |              |  |

|          |                                      |              |  |

|          |                                      | : : : :      |  |

|          | : : : :                              | : : : :      |  |

| ++       | ++                                   | ++           |  |

|          |                                      |              |  |

|          |                                      | : : : :  + 2 |  |

|          |                                      |              |  |

| ++       | ++                                   | ++           |  |

|          |                                      | : : : :  + 3 |  |

|          |                                      |              |  |

|          |                                      |              |  |

| ++       | +   -   -   -   -   +                | ++           |  |

|          |                                      |              |  |

| ++       | ++                                   | ++           |  |

|          |                                      |              |  |

|          |                                      |              |  |

| Board -  | ++++++++++++++++++++++++++++++++++++ |              |  |

|          | 4 3 2 1 0                            |              |  |

|          |                                      |              |  |

## **Power Control**

Boards can be powered on using set\_power():

```

>>> # Power off board (0, 0, 0)

>>> bc.set_power(False)

>>> # Power on board (1, 2, 3)

>>> bc.set_power(True, 1, 2, 3)

```

```

>>> # Power on all 24 boards in frame (1, 2)

>>> bc.set_power(True, 1, 2, range(24))

```

**Note:** Though multiple boards in a single frame can be powered on simultaneously, boards in different frames must be powered on separately.

**Note:** By default the *set\_power()* method adds a delay after the power on command has completed to allow time for the SpiNNaker cores to complete their self tests. If powering on many frames of boards, the *post\_power\_on\_delay* argument can be used to reduce or eliminate this delay.

### **Reading Board Temperatures**

Various information about a board's temperature and power supplies can be read using *read\_adc()* (ADC = Analogue-to-Digital Converter) which returns a *bmp\_controller.ADCInfo* named tuple containing many useful values:

```

>>> adc_info = bc.read_adc() # Get info for board (0, 0, 0)

>>> adc_info.temp_top # Celsius

23.125

>>> adc_info.fan_0 # RPM (or None if not attached)

2401

```

## **Context Managers**

As with *MachineController*, *BMPController* supports the with syntax for specifying common arguments to a series of commands:

```

>>> with bc(cabinet=1, frame=2, board=3):

... if bc.read_adc().temp_top > 75.0:

... bc.set_led(7, True) # Turn on LED 7 on the board

```

## 1.3.3 Sending/receiving SDP and SCP packets to/from applications

A number of low-level facilities are provided for users who wish to send and receive SCP and SDP packets directly. The most common use for these APIs is to send and receive SDP packets to and from a running SpiNNaker application to allow realtime monitoring and communication with the underlying application via an IP Tag. A minimal example of each is presented below.

## Example: Sending SDP packets to a running application

In your SpiNNaker application you should register a callback handler for the arrival of SDP packets. For example, using the spin1\_api:

```

spin1_callback_on(SDP_PACKET_RX, on_sdp_from_host, 0);

```

To send SDP packets to this application, you must open a UDP socket with which to send SDP packets to your SpiNNaker system. Note that (slightly confusingly) SpiNNaker listens for incoming SDP packets on the *SCP* port.

```

>>> import socket

>>> from rig.machine_control.consts import SCP_PORT

>>> out_sock = socket.socket(socket.AF_INET, socket.SOCK_DGRAM)

>>> out_sock.connect((hostname, SCP_PORT))

```

With the port opened, you can use the *rig.machine\_control.packets.SDPPacket* and *rig. machine\_control.packets.SCPPacket* classes to pack your data into properly formatted SDP or SCP packets. Since sark and spin1\_api (unfortunately) make packing/unpacking SDP packets rather clumsy it is common to use SCP packets.

**Note:** SCP packets are just SDP packets with some additional fields placed in the SDP data payload. When a port number other than 0 is used SCP packets are passed to the application like any other SDP packet